锁相环

Clash Royale CLAN TAG#URR8PPP

Clash Royale CLAN TAG#URR8PPP

| 本條目已列出參考文獻,但因為沒有文內引註而使來源仍然不明。 (2016年9月18日) |

鎖相迴路(PLL: Phase-locked loops)是一种利用反馈(Feedback)控制原理实现的频率及相位的同步技术,其作用是将电路输出的时钟与其外部的参考时钟保持同步。当参考时钟的频率或相位发生改变时,鎖相迴路会检测到这种变化,并且通过其内部的反馈系统来调节输出频率,直到两者重新同步,这种同步又称为“鎖相”(Phase-locked)。

目录

1 应用领域

2 组成

3 分类

4 性能指标

5 参考文献

应用领域

鎖相迴路在众多领域有应用,如无线通信、数字电视、广播等。具体的应用范围包括但不限于:

- 无线通信系统收发模块 (Transceiver)

- 数据及时钟恢复电路 (Clock and Data Recovery - CDR)

- 频率综合电路 (Frequency synthesizer)

跳频通信 (Frequency-hopping spread spectrum - FHSS)- 数字电视接收机

组成

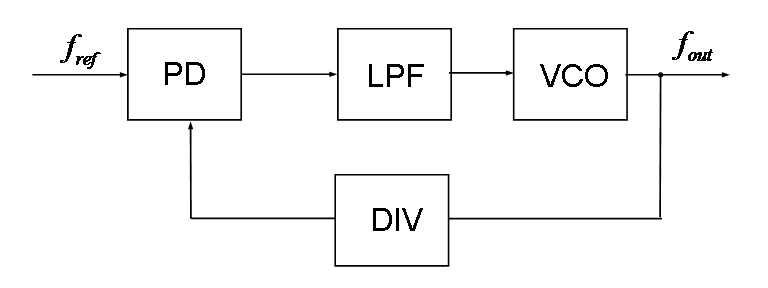

一个鎖相迴路电路通常由以下模块构成:

鉴频鉴相器(PFD)(或鉴相器:PD)

低通滤波器(LPF)

压控振荡器(VCO)- 反馈回路(通常由一个分频器(Frequency divider)来实现)

每个模块的简单原理描述如下:

鉴频鉴相器: 对输入的参考信号和反馈回路的信号进行频率和相位的比较,输出一个代表两者差异的信号至低通滤波器。

低通滤波器: 将输入信号中的高频成分滤除,保留直流部分送至压控振荡器。

压控振荡器: 输出一个周期信号,其频率由输入电压所控制。- 反馈回路 : 将压控振荡器输出的信号送回至鉴频鉴相器。通常压控振荡器的输出信号的频率大于参考信号的频率,因此需在此加入分频器以降低频率。

分类

- 按照实现技术,可以分为模拟鎖相迴路(Analog PLL)和数字鎖相迴路(Digital PLL)。

- 按照反馈回路,可以分为整数倍分频鎖相迴路(Integer-N PLL)和分数倍分频鎖相迴路(Fractional-N PLL)。

- 按照鉴频鉴相器的实现方式,可以分为电荷泵鎖相迴路(Charge-Pump PLL)和非电荷泵鎖相迴路。

- 按照环路的带宽,它可以分为宽带鎖相迴路(Wide band loop PLL)和窄带鎖相迴路(Narrow band loop PLL)。

性能指标

对于鎖相迴路来说,最关键的性能是在于相位雜訊(Phase noise)和动态性能(Dynamics)。

- 鎖相迴路的相位噪声对通信系统的整体性能影响甚大,因此设计中对相位噪声的要求有具体而严格的指标要求。

- 鎖相迴路的动态性能决定了它能够同步参考源的速度和精度,以及在多大范围内能够跟踪参考源。

- 鎖相迴路的动态性能包括:锁定时间(Lock time),捕获范围(Capture range),锁定范围(Hold range)等。

另外,鎖相迴路的稳定性指标包括:环路带宽(Loop bandwidth),相位裕度(Phase margin)等。

参考文献

- D.Banerjee, PLL Performance, Simulation and Design, Fourth Edition, Dog Ear Publishing, LLC, 2006.

- R.E. Best, Phase-Locked Loops: Design, Simulation, and Applications, McGraw-Hill Professional, 2003.

- F.M. Gardner, Phaselock Techniques, Wiley-Interscience, 2005.

- P.R. Gray et coll., Analysis and Design of Analog Integrated Circuits, Wiley, 2001.

- T.H. Lee, The Design of CMOS Radio-Frequency Integrated Circuits, Second Edition, Cambridge University Press, 2003.

- B. Razavi, RF Microelectronics, Prentice Hall, 1998.

- K. Shu et E. Sánchez-Sinencio, CMOS PLL Synthesizers: Analysis and Design, Springer, 2004.

- Predicting the Phase Noise and Jitter of PLL-Based Frequency Synthesizers

- MIT Open Course: 6.976 High Speed Communication Circuits and Systems, Spring 2003

- William F. Egan, Phase-Lock Basics, Wiley-IEEE Press, 2 edition, November, 2007

- William F. Egan, Frequency Synthesis by Phase Lock, Wiley-Interscience, 2 edition December,1999

- Circuit sage: Phase Locked Loop Design

- Dennis Fischette's 1-Stop PLL Center

- Ask the Applications Engineer - 30 - PLL Synthesizers

- Jess Chen,“An introduction to the PLL library”, Cadence Design Systems document

- Agilent EEsof EDA Applications: Phase-Locked Loops

PhD thesis: Modeling and simulation techniques for the accurate verification of Integer-N PLLs[永久失效連結]

|